ProcessorTechnology

# I6 KRA DYNAMIC READ/WRITE MEMORY MODULE USER'S MANUAL

ProcessorTechnology Corporation

7100 Johnson Industrial Drive Pleasanton, CA 94566 Telephone (415) 829-2600

# TABLE OF CONTENTS

| SECTION |       |                                         | PAGE                            |

|---------|-------|-----------------------------------------|---------------------------------|

| I       | INTRO | DDUCTION AND GENERAL INFORMATION        |                                 |

|         | 1.1   | Introduction                            | 1-1                             |

|         | 1.2   | General Information                     | 1-1                             |

|         |       | 1.2.2 Receiving Inspection              | 1-1<br>1-1<br>1-2<br>1-2<br>1-2 |

| II      | HANDI | LING PRECAUTIONS AND BOARD LAYOUT       |                                 |

|         | 2.1   | Handling Precautions                    | 2-1                             |

|         |       | 2.1.1 Installing And Removing The 16KRA | 2-1                             |

|         | 2.2   | Board Layout                            | 2-2                             |

|         |       |                                         | 2-2                             |

| III     | OPERA | ATIONAL TEST                            |                                 |

|         | 3.1   | 16KRA Checkout Procedure                | 3-1                             |

|         | 3.2   | Pre-operational Check                   | 3-1                             |

|         | 3.3   | Memory Test                             | 3-1                             |

| IV      | OPTIC | ON SELECTION                            |                                 |

|         | 4.1   | Option Selection                        | 4-1                             |

|         | 4.2   | Waiting Time Option (Area A)            | 4-1                             |

|         | 4.3   | Power-up Initialization Option (Area B) | 4-1                             |

|         | 4.4   | Memory Disable Option (Area C)          | 4-2                             |

|         | 4.5   | DMA Option (Area D)                     | 4-2                             |

|         | 4.6   | Ready Line Option (Area E)              | 4-3                             |

|         | 4.7   | Starting Address                        | 4-3                             |

| V       | THEOR | RY OF OPERATION                         |                                 |

|         | 5.1   | Overview                                | 5-1                             |

|         | 5.2   | S-100 Bus Signals                       | 5-2                             |

|         | 5.3   | Detailed Description                    | 5-2                             |

|         |       | 5.3.2 Memory Array And Drivers          | 5-2<br>5-4<br>5-5<br>5-10       |

|         | 5.4   | Refresh                                 | 5-13                            |

| REV A   |       | ÷                                       |                                 |

i

# TABLE OF CONTENTS (Continued)

| SECTION |       |                 |                      |         |     |       |      |     |      |     |     |     |    |    |   | PAGE       |  |

|---------|-------|-----------------|----------------------|---------|-----|-------|------|-----|------|-----|-----|-----|----|----|---|------------|--|

| VI      | DRAW: | INGS            |                      |         |     |       |      |     |      |     |     |     |    |    |   |            |  |

|         |       |                 | bly Draw             | ing .   |     |       |      |     |      |     |     | ,   |    |    |   | 6-1        |  |

|         |       |                 | atic Dia             |         |     |       |      |     |      |     |     |     |    |    |   | 6-2        |  |

|         |       |                 | Diagram              |         |     |       |      |     |      |     |     |     |    |    |   | 6-3        |  |

|         |       |                 |                      |         |     |       |      |     |      |     |     |     |    |    |   |            |  |

|         |       |                 |                      |         |     |       |      |     |      |     |     |     |    |    |   |            |  |

| VII     |       | NOSTIC          |                      |         |     |       |      |     |      |     |     |     |    |    |   |            |  |

|         | 7.1   |                 | UCTION.              |         |     | •     |      | •   | •    | ٠   | ٠   | e   | •  | •  |   | 7-1        |  |

|         |       |                 | General              |         |     | •     |      |     |      |     | -   |     |    | •  |   | 7-1        |  |

|         |       |                 | Data Pa<br>Address   |         |     |       |      |     |      | •   | •   | •   |    | -  |   | 7-1<br>7-1 |  |

|         |       |                 | Exercise             |         |     | •     | •    | •   | •    | •   |     | •   | •  | •  | , | 7-2        |  |

|         |       |                 | Numbere              |         |     | elect | cion | 1 - | Ţ    |     |     | -   |    |    |   | 7-2        |  |

|         | 7.2   |                 | UCTION TO            |         |     |       |      |     |      |     |     |     |    |    |   | 7-2        |  |

|         | 7.3   |                 | INARY TE             |         |     |       |      |     |      |     |     |     |    |    |   | 7-3        |  |

|         | 7.4   |                 | KDT TEST             |         |     |       |      |     |      |     |     |     |    |    |   | 7-4        |  |

|         | 7 5   | OVERVI          |                      |         |     |       |      |     |      |     |     |     |    |    |   | 7-6        |  |

|         | , ,,  |                 | Board S              | 2]00+   |     | •     |      | •   |      | •   |     |     |    | •  | • | 7-6        |  |

|         |       |                 | MC.                  | STECT   | •   | a     |      |     |      | •   | 49  |     | •  | •  | • | 7-6        |  |

|         |       | 7.5.3           | SR.                  |         |     |       |      |     |      |     |     |     |    |    |   | 7-8        |  |

|         |       | 7.5.4           | RC                   |         |     |       | ,    |     |      |     | a   |     |    |    |   | 7-8        |  |

|         |       | 7.5.5           | CY                   |         |     |       |      |     | 3    | 2   | e   | ×   |    |    |   | 7-8        |  |

|         |       |                 | WE                   | e e     | *   |       |      |     | •    |     |     | ×   |    |    | • | 7-8        |  |

|         |       | 7.5.7           |                      |         |     | •     |      |     |      | •   |     | *   | *  |    | ٠ | 7-8        |  |

|         |       |                 | CAE .                |         |     | •     | •    |     |      | ٠   |     | ٠   | •  | ٠  |   | 7-8        |  |

|         |       | 7.5.9<br>7.5.10 | CAS .                |         | •   | •     | •    | •   | •    | ٠   | ۰   | ۰   | -0 | •  |   | 7-8<br>7-8 |  |

|         |       |                 | Output               | Fnahl   |     | 4     |      | a   |      | •   |     | •   |    | •  |   | 7-8        |  |

|         | 7.6   | BUS CR          | -                    | DIIGD I |     | •     | •    | a   |      |     | •   | _   |    |    |   | 7-8        |  |

|         |       |                 |                      |         | (8  | •     | •    | •   | •    | •   | •   | •   | ٠  | •  |   |            |  |

|         | / . / |                 | M CHIP.              |         |     |       |      |     |      |     |     |     |    |    |   |            |  |

|         |       |                 | Overview<br>Trouble: |         |     |       |      |     |      |     |     |     |    |    |   |            |  |

|         | 7.8   | THE WR          | ITE REQU             | EST FI  | LIP | FLOF  |      | •   | •    | a   |     |     | ,  | •  | s | 7-13       |  |

|         | 7.9   | WRITE :         | ENABLE O             | PERAT   | ION | - WE  |      |     |      |     |     |     |    |    |   | 7-14       |  |

|         | 7.10  | MACHIN          | E CYCLE              | - MC.   |     | ,     |      |     |      |     |     |     |    |    |   | 7-14       |  |

|         | 7.11  | CYCLE           | FLIP FLO             | 5 - C2  | ζ.  |       | ,0   |     |      |     |     | o   |    |    |   | 7-14       |  |

|         | 7.12  | SYNCHR          | ONOUS REI            | FRESH   | - 5 | GR.   |      |     |      |     |     |     |    |    |   | 7-15       |  |

|         | 7.13  | THE AL          | LOW REFRI            | ESH FI  | LIP | FLOF  |      | AR  |      |     |     |     |    | .0 |   | 7-15       |  |

|         | 7.14  | PAGE S          | ELECTION             |         |     |       |      | •   | g    | •   |     | •   | •  |    |   | 7-16       |  |

|         |       |                 | Overvie              |         |     |       |      |     |      |     |     |     |    |    |   |            |  |

|         |       | 7.14.2          | Troubles             | shooti  | ing | The   | Pag  | e S | Sele | ect | Cir | cui | t  | e  |   | 7-16       |  |

REV A ii

# TABLE OF CONTENTS (Continued)

| SECTION |                                                                  |        |   | PAGE              |

|---------|------------------------------------------------------------------|--------|---|-------------------|

|         | 7.15 READY LINE                                                  |        |   | . 7-18            |

|         | 7.15.1 Queue Operation - QU                                      |        |   | . 7-18            |

|         | 7.16 THE WAIT STATE OPTION                                       |        |   | . 7-20            |

|         | 7.17 REFRESH CYCLE FLIP FLOP - RC                                |        |   | . 7-20            |

|         | 7.18 THE REFRESH CIRCUIT                                         |        |   | . 7-21            |

|         | 7.18.1 Overview                                                  |        |   | . 7-21            |

|         | 7.18.2 Troubleshooting Refresh                                   |        | • | . 7-2]            |

|         | APPENDICES                                                       |        |   |                   |

| 1       | Statement of Warranty                                            |        |   |                   |

| 2       | 8080 Operating Codes                                             |        |   |                   |

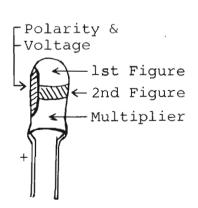

| 3       | Color Codes for Resistors And Capacitors                         |        |   |                   |

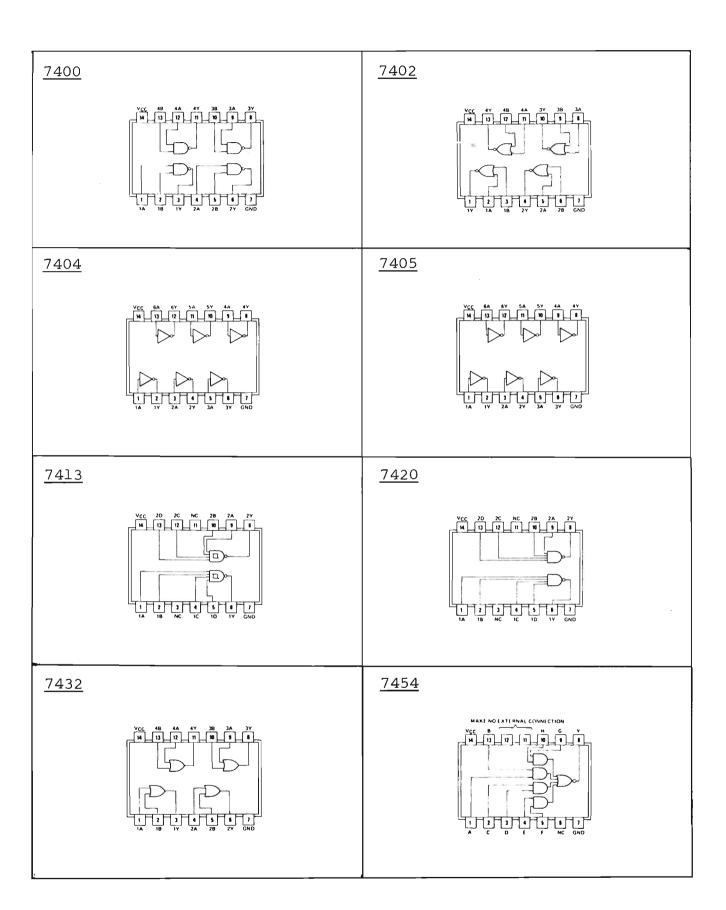

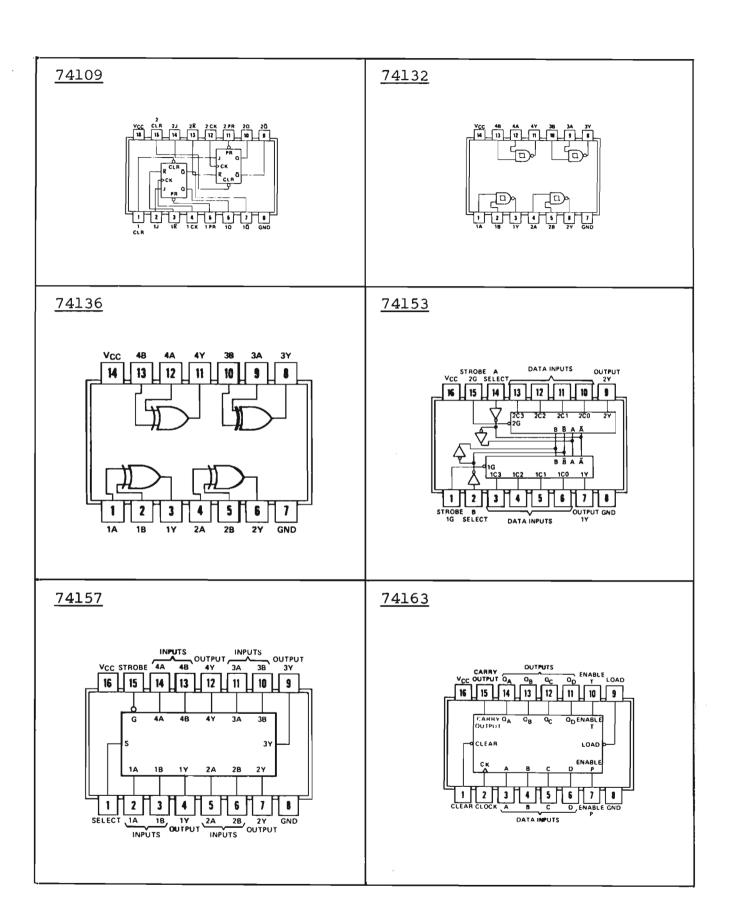

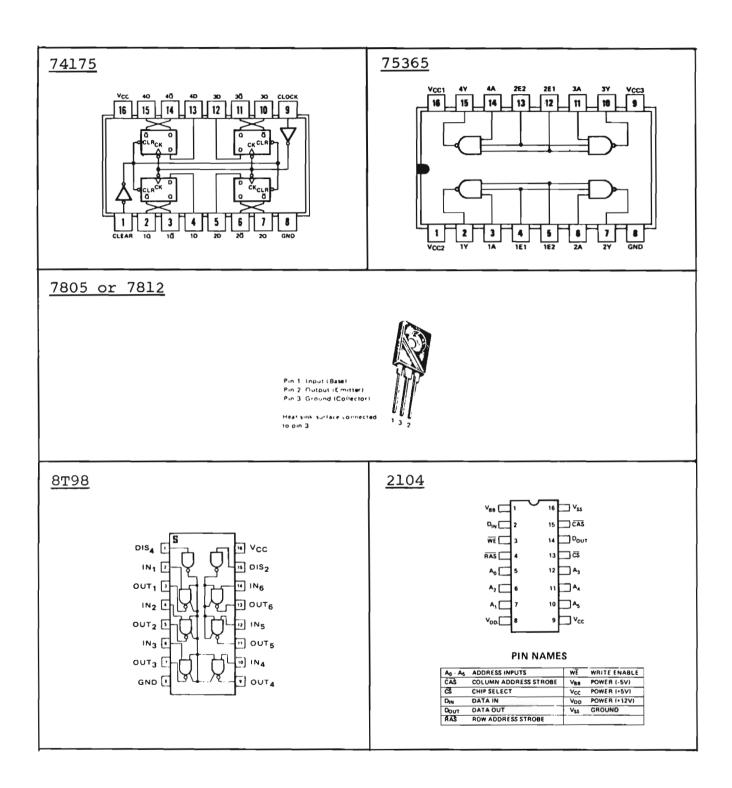

| 4       | IC Pin Configurations                                            |        |   |                   |

| 5       | Memory Test Program                                              |        |   |                   |

|         | TABLES                                                           |        |   |                   |

| 41      | 16KRA Starting Address Selection                                 |        | • | . 4-1             |

| 5-1     | Summary of S-100 Bus Signals And Their Use .                     |        | • | . 5-3             |

| 7-1     | Test Addresses                                                   |        | • | . 7-2             |

| 7-2     | Resistance Measurements at RAM Pins                              | • •    | • | 7 – 4             |

| 7-3     | Bus Line - IC Pin Signal Checks                                  |        | • | . 7-9             |

| 7 – 4   | LS136 Pin Assignments                                            |        | • | . 7-18            |

| 7-5     | Counter Periods                                                  | • •    | • | . 7-2]            |

| 2-1     | Page And Bit Assignments in Memory Array                         |        |   | . 2-3             |

| 4-1     | Page And Address Line Assignments for Address Selection Switches |        |   | . 4-4             |

| 7-1     | Connector Jumpers                                                | • .    |   | . 7-3             |

| 7-2     | Address Switch Positions                                         |        |   | <sub>*</sub> 7-5  |

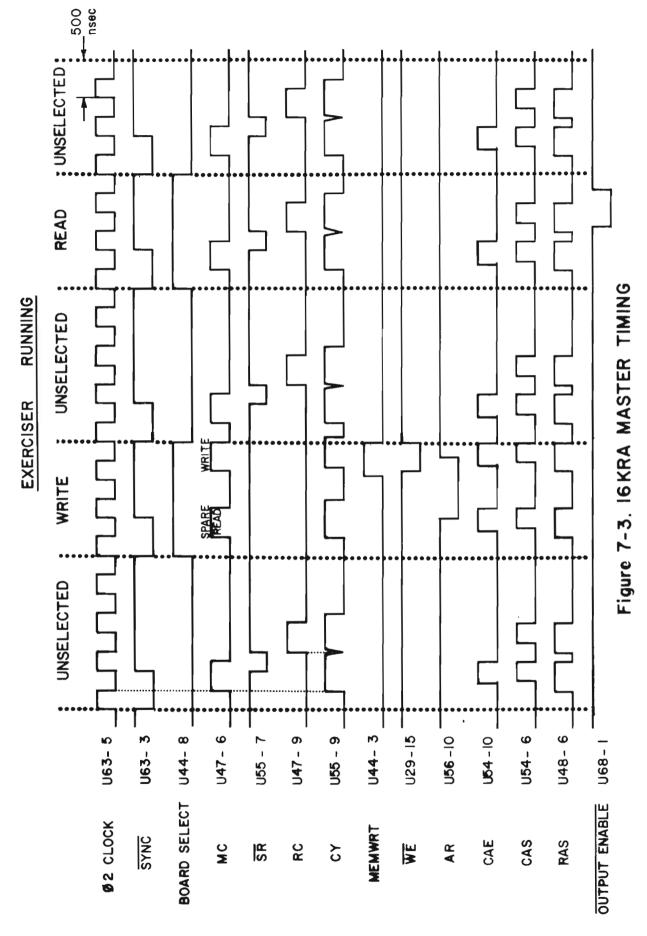

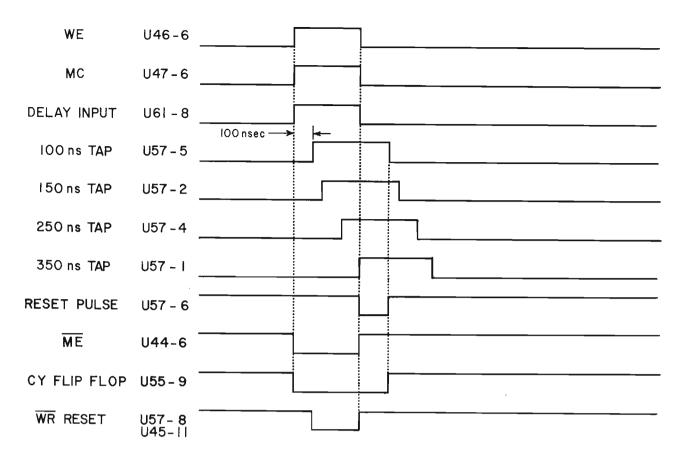

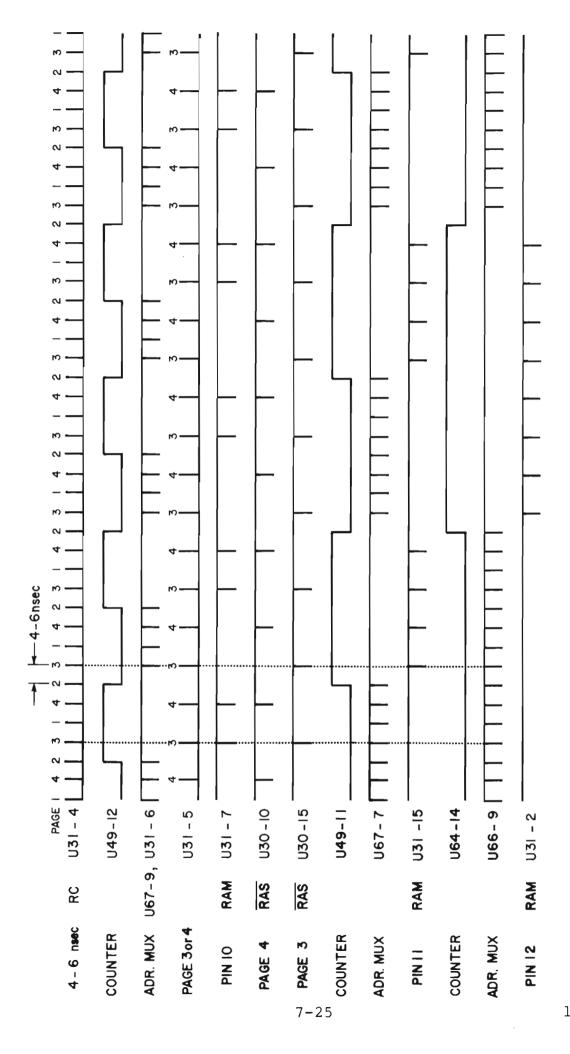

| 7 - 3   | 16KRA Master Timing                                              |        |   | . 77              |

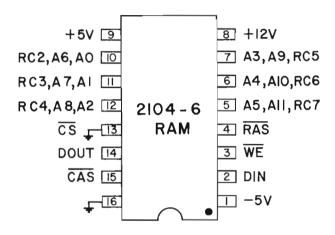

| 7 - 4   | RAM Chip Pin Assignments                                         |        |   | . 7-12            |

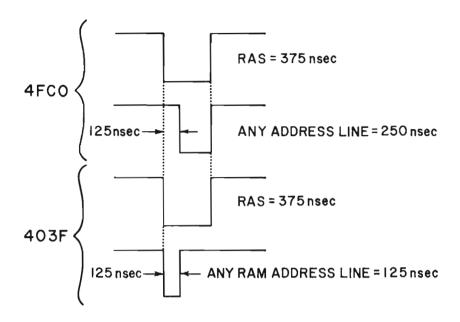

| 7-5     | RAM Address Signal Waveforms                                     |        |   | . 7-13            |

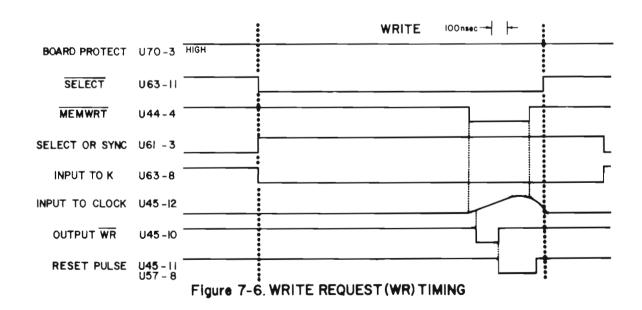

| 7 – 6   | Write Request (WR) Timing                                        |        |   | . 7-13            |

| 7-7     | Cycle (CY) Timing                                                |        |   |                   |

| 7-8     | MEMWRT Pulse Pattern                                             | . , 20 |   | . 7-16            |

| 7-9     | Refresh Page Selection Timing                                    |        |   | . 7-23            |

| 7-10    | RAM Address Line Timing During Refresh.                          | . ,    |   | - 7-24            |

| 7-11    | RAM Refresh Timing - Page 3 and 4                                |        |   | <sub>*</sub> 7-25 |

REV A iii

| · |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

# SECTION I

# INTRODUCTION AND

# GENERAL INFORMATION

#### 1.1 INTRODUCTION

This manual supplies the information needed to test and use the 16KRA Dynamic Read/Write Memory Module. So that you can use your module most effectively and safely, we suggest that you read the entire manual before attempting to use the 16KRA.

Should you encounter any problem in using the 16KRA, first consult the manual for a possible solution. If you are unable to find the solution, feel free to ask for our help.

# 1.2 GENERAL INFORMATION

# 1.2.1 16KRA Memory Description

The 16KRA Dynamic Read/Write Memory Module has a capacity of 16,384 eight bit words and operates in a dynamic mode. Periodic refreshing is done automatically by the module.

It is designed to operate in the Sol S-100 bus and a number of other 8080 based computers such as the Altair 8800 and IMSAI 8080. Lines interfacing to the S-100 bus are fully buffered, and extensive noise immunity circuitry is used.

The 16KRA features switch selectable address selection. It is organized into four "pages" of 4096 bytes each. Each page may be independently assigned to any of 16 starting addresses at 4096 byte intervals, starting with address  $\emptyset\emptyset\emptyset\emptyset$  (hexadecimal).

This module will operate in Sol and other 8080 based computers which have a 2 MHz Ø2 rate without imposing wait states during normal operation. Access and cycle times are 400 and 520 nsec respectively.

The 16KRA Memory requires +7.5 to +10 V dc at 0.8 amp max., +15 to +18 V dc at .15 amp max., and -15 to -18 V dc at .02 amp max. An on-board battery connector is also included for connecting standby power to provide long term data retention during power loss.

## 1.2.2 Receiving Inspection

When your module arrives, examine the shipping container for signs of possible damage to the contents during transit. Then inspect the contents for damage. (We suggest you save the shipping materials for use in returning the module to Processor Technology should it become necessary to do so.) If your 16kRA is damaged, please write us at once describing the condition of both the shipping container and its contents so that we can take appropriate action.

## 1.2.3 Warranty Information

In brief, the parts used on your 16KRA and the module itself are warranted against defects in materials and workmanship for a period of one year following the date of purchase. Refer to Appendix I for the complete "Statement of Warranty".

## 1.2 4 Replacement Parts

Order replacement parts by Processor Technology part number, component nomenclature (e.g., DM8131) and/or a complete description (e.g., 6.8 ohm, ½ watt, 5% resistor).

# 1.2.5 Factory Service

In addition to in-warranty service, Processor Technology also provides factory repair service on out-of-warranty products. Before returning the unit to Processor Technology, first obtain our authorization to do so by writing us a letter describing the problem. After you receive our authorization to return the unit, proceed as follows:

- 1. Write a description of the problem.

- 2. Pack the unit with the description in a container suitable to the method of shipment.

- 3. Ship prepaid to Processor Technology Corporation.

Your unit will be repaired as soon as possible after receipt and shipped to you prepaid. (Factory service charges will not exceed \$20.00 without prior notification and your approval.)

# SECTION II

# HANDLING PRECAUTIONS

AND

BOARD LAYOUT

# 2.1 HANDLING PRECAUTIONS \*\* IMPORTANT \*\*

Though the 16KRA is already assembled and tested, you may have a future need to replace components and/or make measurements on the board. Integrated circuits (IC's) can be damaged by improper handling. Also, the module itself can be damaged by indiscriminate use of clip test leads as well as improperly installing it in, or removing it from, the computer.

It is important, therefore, that you carefully read and observe the following precautions before testing or using the 16KRA or replacing any IC.

## 2.1.1 Installing and Removing the 16KRA

To avoid any possible static electricity discharge damage to the MOS elements used on the 16KRA, always place one hand on the computer chassis before touching the module and use your other hand for the module. (Just remember to handle the module so that no discharge flows through it and you 11 do fine.) This precaution holds true whether you are installing or removing the 16KRA.

NEVER install the 16KRA in, or remove it from, the computer with the power on. To do so can damage the module or the computer.

When installing the module, first make sure that you have it oriented correctly in relation to the bus pins. That is, be sure that pin 1 on the module edge connector mates with pin 1 of the bus connector. (If you install it reversed, you can damage the 16KRA or computer when power is turned on.) Slide module into card guides until its edge connector just enters the bus connector. Then push on module until it is fully seated in the bus connector.

### 2.1.2 Handling MOS Integrated Circuits

The memory IC's used on the 16KRA are MOS devices. They can be damaged by static electricity discharge. Always handle MOS IC's so that no discharge will flow through the IC. Also, avoid unnecessary handling and wear cotton--rather than synthetic--clothing when you do handle these IC's.

# 2.1.3 Installing and Removing Integrated Circuits

NEVER install or remove integrated circuits while power is applied to the 16KRA. To do so can damage the IC.

### 2.1.4 Use of Clip Leads

Clip leads attached to the ends of the module are apt to short to IC pins.

(Continued on Page II-2.)

Always attach ground clips to the <u>lower</u> edge of the board near edge connector pin 50 which is located at the right end of the connector when the board is oriented as specified in Paragraph 2.2.1. (A terminal (wire) is attached to pin 50 to provide a convenient grounding point.)

#### NOTE

The heat sink bar is a poor ground since its finish is nonconducting.

#### 2.2 BOARD LAYOUT

## 2.2.1 Orientation

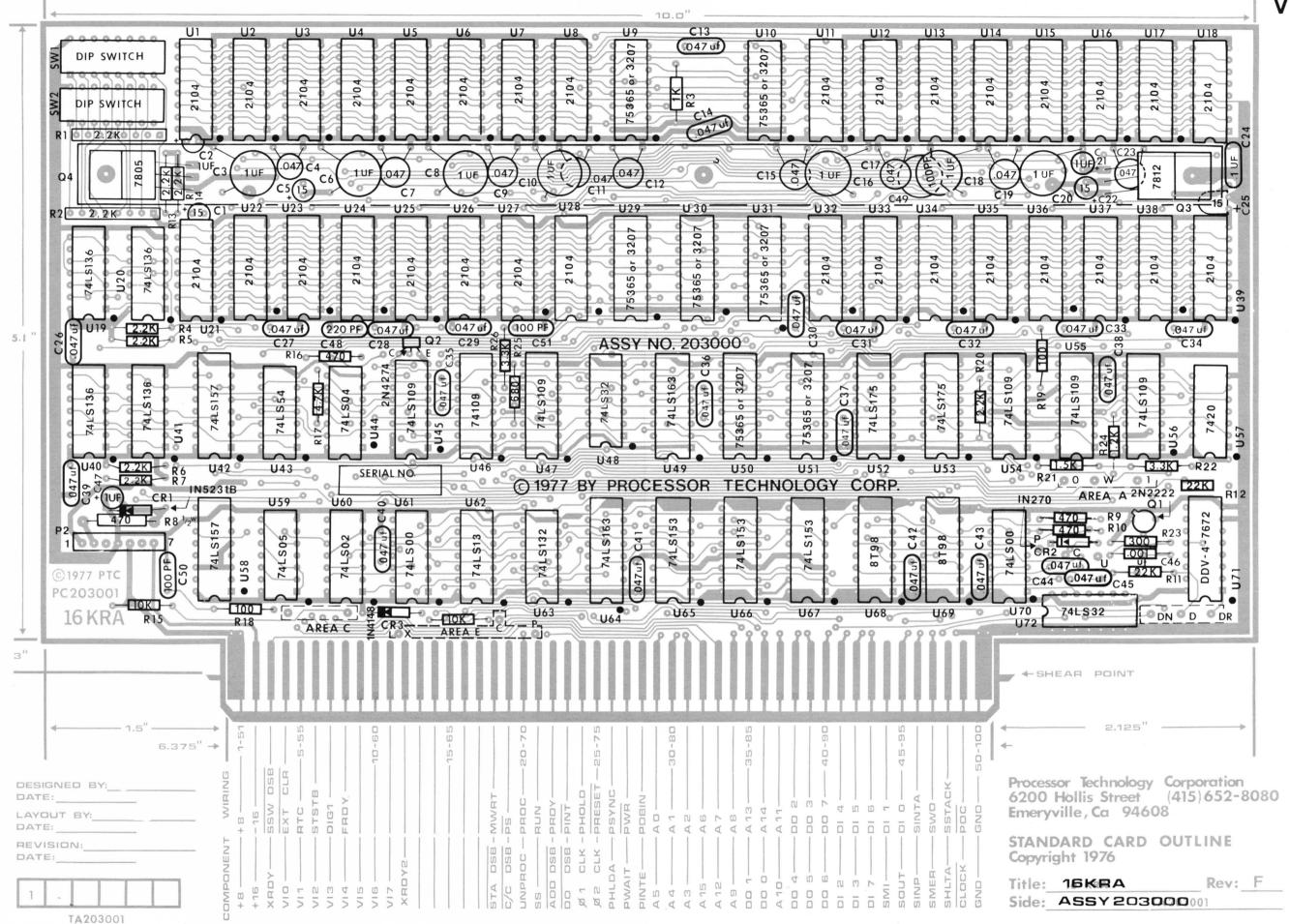

With the component (front) side of the module facing up and the edge connector at the bottom, the heat sink bar will be near the top edge of the circuit board. Subsequent position references in the next paragraph assume this orientation. (See Assembly Drawing in Section VI, page VI-1.)

#### 2.2.2 Layout

On the component side of the board, edge connector pin 1 is at the left end of the connector and pin 50 is at the right end. Pins 51 and 100 are at the left and right ends respectively on the solder (back) side.

In the upper left corner are the address (page) selection switches. (See Section IV for the page and address line assignments for these switches.) Across the top half of the module is the memory array, two rows of 32 memory IC's separated in the middle by five drivers. Figure 2-1 shows the page and bit assignments for the memory IC's. The heat sink bar runs across the board between the two rows of memory IC's.

Moving down to the lower half of the board you see all of the control logic for the 16KRA. In the lower left corner is the battery backup power connector.

2-2 16KRA

Figure 2-1. Page And Bit Assignments in Memory Array

N39 U18 Bit 7 Bit 7 Pg 2 Pg 4 Bit 7 Bit 7 U38 117 Pg 3 Pg 016 Bit 6 Bit 6 **U37** Pg 2 Pg 4 Bit 6 N36 Bit 6 2 Pg 1 Pg 3 UL **U14** Bit 5 Bit 5 U35 Pg 2 Pg 4 Bit 5 Bit 5 034Pg 1 Pg 3 Ul Bit 4 U33 **U12** Bit 4 Pg 2 Pg 4 Bit 4 Bit 4 U11 **U32** Pg 1 Pg 3 BOARD OF Bit 3 U28 Bit 3 TOP 108 Pg 2 Pg 4 Bit 3 U27 Bit 3 Pg 1 Pg 3 U7 Bit 2 Bit 2 **U26** 90 Pg 2 Pg 4 Bit 2 **U25** Bit 2 05Pg 3 ₽g Bit **U24** Bit 1 U4 Pg 2 Pg 4 Bit Bit 1 U23 03Pg Pg 3 Bit U22 Bit Pg 4 U2 Pg 2 Bit Bit U2.1 Pg 3 Ul Pg

|  |  | $\overline{}$ |

|--|--|---------------|

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  | $\bigcirc$    |

|  |  |               |

|  |  |               |

# SECTION III

# OPERATIONAL TEST

#### 3.1 16KRA CHECKOUT PROCEDURE

Your 16KRA Memory Module is fully inspected and tested before shipment to insure that it is operating correctly and that it meets specifications. It is then packaged for safe transit under normal shipping conditions. Your module should, therefore, arrive in your hands ready for use.

We nevertheless recommend that you precheck your 16KRA as outlined in the following paragraphs before using it.

#### 3.2 PRE-OPERATIONAL CHECK

Before installing the module in your computer, visually inspect it for obvious physical damage. Also check that all integrated circuits (IC's) are fully seated in their sockets. If physical damage exists, follow the instructions given in Section I, Paragraph 1.2.2. If your inspection reveals no problems, proceed with the memory test.

# 3.3 MEMORY TEST

Install the 16KRA in your computer and test it for proper operation. Test programs and instructions for testing the module are provided in Appendix V.

#### CAUTION

NEVER INSTALL OR REMOVE 16KRA WITH COMPUTER POWER ON.

3-1 16KRA

# SECTION IV

# OPTION SELECTION

#### 4.1 OPTION SELECTION

Jumper options that control five operating parameters are provided on the 16KRA Memory Module. They are: waiting time, power-up initialization, phantom memory disable, DMA waiting time, and ready line option. The starting address for each page is switch-selectable. Use the following option selection instructions in conjunction with the assembly drawing in Section VI.

#### NOTE

We recommend you use #24 bare wire for jumpers. Simply bend a small loop of wire and insert about 1/4 inch of wire into each Augat pin.

# 4.2 WAITING TIME OPTION (AREA A)

Since the 16KRA operates at maximum speed, you normally will not enable the waiting time option. To configure the 16KRA for no waiting time, install a jumper between the W and  $\emptyset$  pins in Area A.

For special applications, you may want to enable the waiting time option which provides one wait state that is 0.5 usec long. To enable the wait state, install a jumper between the W and 1 pins in Area A.

# 4.3 POWER-UP INITIALIZATION OPTION (AREA B)

The jumper arrangement in <u>Area B</u> determines whether the 16KRA will come up in the protected or unprotected mode when power is initially applied or restored after a power failure. In the protect mode a random operation cannot improperly rewrite retained data.

To select the power-up protect  $\underline{mode}$ , install a jumper between the CLR and P pins in  $\underline{Area}$   $\underline{B}$ .

To select the <u>power-up unprotect mode</u>, install a jumper between the CLR and U pins in <u>Area B</u>.

#### NOTE

If your computer does not use the PROT (protect) and UNPROT (unprotect) lines, PROT (S-100 Bus pin 70) must be connected to zero volts.

## 4.4 MEMORY DISABLE OPTION (AREA C)

Select the phantom option if the 16KRA will be used at address Ø in conjunction with a system which uses a phantom start-up procedure, such as the Processor Technology Sol, GPM, or ALS-8 Firmware Module. To enable this option, install a jumper between the two pins in Area C. With this jumper installed, the 16KRA will be disabled by the signal PHANTOM, supplied on S-100 pin 67.

If the 16KRA is not to be used at address  $\emptyset$ , or is not to go in a system using phantom start-up, do not install the jumper.

# 4.5 DMA OPTION (AREA D)

The jumper arrangement in <u>Area D</u> determines when the refresh timer (Ql and U63-8) is reset to zero. Two options are available.

The first, DN, is normally used. With this option selected, the refresh timer is reset to zero at every refresh cycle. A DMA device which sends no read request for 6 usec will encounter a wait state while refresh is done. With this option a DMA device must observe PRDY or be prepared to accept data errors if its requests are coincident with spontaneous refresh. To select this option, install a jumper between the D and DN pins in  $\underline{\text{Area }D}$ .

If DR is enabled ...

- ...the refresh timer is reset to zero after read and write cycles as well as after refresh cycles.

- ...a DMA device which sends a read or write request within 6 useconds will not encounter wait states.

- ...loss of refresh may occur on long DMA transfers that contain no read requests.

To enable this option, install a jumper between the D and DR pins in Area  $\underline{D}$ .

DO NOT select this option unless it is absolutely necessary. If you do use this option, remember that REFRESH IS THE RESPONSIBILITY OF THE DMA DEVICE. Check with us before using the DR option.

### 4.6 READY LINE OPTION (AREA E)

The 16KRA requires a wait period under certain unusual circumstances. The wait period is generated when pin 23, Ready, of the 8080 microprocessor is pulled low. The Ready line is driven by S100 bus signals XRDY (pin 3) and PRDY (pin 72). Different computers require the use of one of these two signals with their memory boards. Consult the manual for your computer to determine which to use. (The Sol Terminal Computer uses PRDY.)

To select PRDY, jumper pin C to pin P in Area E. To select XRDY, jumper pin C to pin X in Area E.

## NOTE

Revision D and E 16KRA circuit boards are wired for the PRDY option only. Connection to XRDY may be made by cutting a trace and soldering a jumper in place.

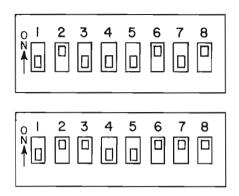

# 4.7 STARTING ADDRESS

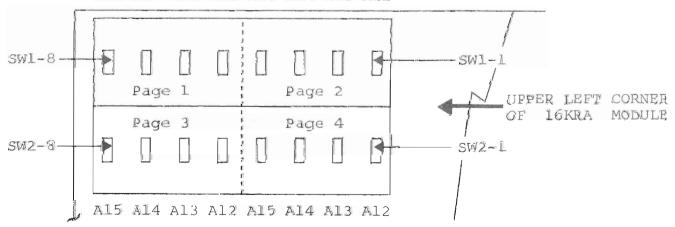

Each of the four 4096 byte pages in the 16KRA can be independently addressed with the dual inline (DIP) switches located in the upper left corner of the module (board oriented as specified in Section II). Page and address line assignments for these switches are shown in Figure 4-1 on page IV-4.

You can assign the same starting address to two, three or all four pages on one 16KRA module with no ill effect.

In general, you may not assign any memory space to a 16KRA that is already assigned to another 16KRA module—or any other memory module—if they are to share the same bus simultaneously. To do so will cause the bus drivers to "fight" for possession of the bus which will result in improper operation or damage. (One exception to this general rule is if you enable the phantom memory disable option which allows the ALS—8 to share address zero with a 16KRA.)

To select the desired starting address for a page, set the four DIP switches associated with the page as shown in Table 4-1 on page IV-4. (Only the indicated starting addresses are available. No intermediate addresses can be used.)

Table 4-1. 16KRA Starting Address Selection.

| STARTING ADDRESS                           |      | DIP SWITCH SETTINGS |     |     |     |

|--------------------------------------------|------|---------------------|-----|-----|-----|

| Decimal                                    | Hex  | A15                 | A14 | A13 | Al2 |

| 0                                          | 0000 | Х                   | X   | Х   | Х   |

| 4,096                                      | 1000 | X                   | X   | X   | C   |

| 8,192                                      | 2000 | Х                   | X   | C   | X   |

| 12,288                                     | 3000 | X                   | X   | C   | C   |

| 16,384                                     | 4000 | Х                   | C   | X   | X   |

| 20,480                                     | 5000 | Х                   | C   | X   | C   |

| 24,576                                     | 6000 | X                   | C   | C   | X   |

| 28,672                                     | 7000 | X                   | C   | C   | C   |

| 32,768                                     | 8000 | С                   | X   | X   | X   |

| 36,864                                     | 9000 | С                   | X   | X   | C   |

| 40,960                                     | A000 | C                   | X   | C   | X   |

| 45,056                                     | в000 | C                   | X   | C   | C   |

| 49,152                                     | C000 | C                   | C   | X   | X   |

| 53,248                                     | D000 | C                   | C   | X   | C   |

| 57,344                                     | E000 | С                   | C   | C   | X   |

| 61,440                                     | F000 | C                   | С   | C   | C   |

| X = switch open, or OFF (in down position) |      |                     |     |     |     |

| C = switch closed, or ON (in up position)  |      |                     |     |     |     |

A15 A14 A13 A12 A15 A14 A13 A12

Figure 4-1. Page And Address Line Assignments for Address Selection Switches.

# SECTION V

# THEORY OF OPERATION

#### 5 1 OVERVIEW

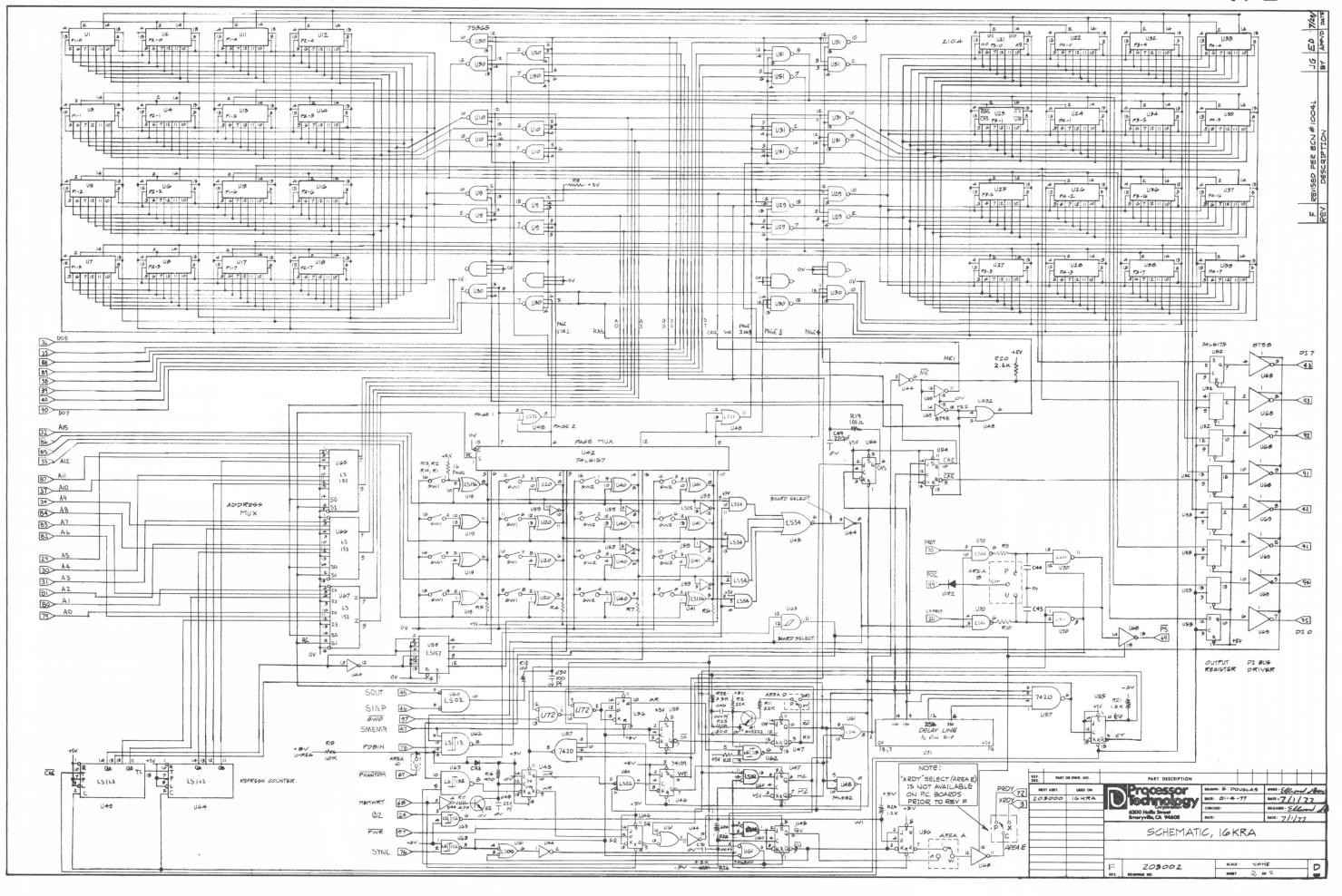

Refer to 16KRA schematic in Section VI, page VI-2, and 16KRA Block Diagram, page VI-3.

In the 16KRA a cycle is a timed sequence of events that perform one memory access. There are six kinds of cycles--read, write, refresh, unselected, coincidence and null--and all are initiated by RC or MC. One or a group of cycles intended to accomplish a desired result is called an "operation". A number of operation types are possible in the 16KRA, but there are four intended operations: read, ready write, unready write and spontaneous refresh. All other operations are variations of the intended operations and result from asynchronous coincidence between intended operations.

Since the memory IC's (2104) used in the 16KRA are dynamic memories in which the data cells operate by stored electrical charge, stored data must be read and restored periodically. Otherwise, current leakage would eventually change the stored data. The restoring process is called "refreshing" the memory, or simply "refresh".

The 16KRA provides memory refresh as required without any external intervention. In most cases it is done without introducing any delay to the CPU or DMA device controlling the module.

Address lines Al2-Al5 are compared to four sets of four switches to select one or none of four 4K memory arrays called "pages". Each page consists of eight 2104 memory IC's.

Address lines AØ-11 are applied to a four-input multiplexer (U65-U67) in two groups of six. These two groups are selected in succession to the memory address drivers (U10, U31, parts of U9, U29), which drive the memory address inputs.

Row Address Strobe (RAS) is applied to the eight memory IC's of the selected page. Its leading edge causes these eight IC's to store the first group of six address bits (AØ-A5), called the row address, and to start a memory cycle.

Subsequently, column address strobe (CAS) is applied to all of the memory IC's. It causes them to release their data outputs to the 3rd state (open circuited). Its leading edge causes those selected by RAS to store the second group (A6-All), called the column address.

CAS samples Write Enable  $(\overline{WE})$  to determine whether this cycle is to write data into memory, or read data from memory.

The contents of the Data Out Bus (DOØ-DO7) are applied to the Data In pins of the memory array by eight Memory Data drivers (U50, U51). One bit from the Data Out bus is applied to four memory IC's, one in each of the four pages.

In a memory write operation, CAS causes the selected eight memory IC's to store the data found on their Data In pins in an input latch. This data is subsequently stored at the location described by the row and column addresses.

In a memory read operation, the selected eight memory IC's receive data from the address indicated, send it to their output latches, and enable their output drivers.

Shortly after the end of RAS and CAS, the read data is latched into the output register (U52,U53), and sent to the Data In Bus (DIØ-DI7) by the DI Bus Drivers (U68,U69) if these are enabled.

Addressing is summarized here:

AØ -A5 Selects Row inside memory chips

A6 -All Selects Column inside memory chips

Al2-Al5 Selects one (or none) of four pages and selects (or deselects) this board.

### 5.2 S-100 BUS SIGNALS

The host machine and 16KRA communicate with one another over the S-100 Bus. Table 5-1 identifies these signals and their source and defines their function.

### NOTE

The 16KRA ignores all S-100 Bus signals except those listed in Table 5-1.

#### 5.3 DETAILED DESCRIPTION

#### 5.3.1 Page and Board Selection

Page and board selection depends on address bits Al2-Al5 and on four groups of four switches.

Each group of four switches describes one of 16 possible starting addresses. Each group of four switches corresponds to one page of eight memory IC's.

The contents of each group of four switches is compared to address bits Al2-Al5 by four open collector exclusive OR gates (Ul9, U20,U40,U41). If a match is found, the (wire AND'ed) output line common to that group of four is allowed to rise. These four lines are called match lines.

5-2 16KRA

Table 5-1. Summary of S-100 Bus Signals and Their Use.

| SIGNAL                | SOURCE    | FUNCTION                                                                                                                                                                 |

|-----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMWRT                | Computer  | Leading edge may initiate write operation.                                                                                                                               |

| PSYNC                 | Processor | Trailing edge may request a read or refresh cycle, and may erase a deferred request (reset QU) or prevent a refresh.                                                     |

| Ø2                    | Computer  | Trailing edge during SYNC or QU sets QU (deferred) if a cycle is in process, or clears QU and starts a read cycle if no cycle is in process. It also clocks wait binary. |

| D0Ø-7                 | Processor | Data source for write operation.                                                                                                                                         |

| AØ-11                 | Processor | Address source for memory array.                                                                                                                                         |

| Al2-15                | Processor | Input source for page and board selection.                                                                                                                               |

| SINP                  | Processor | Inhibits board selection.                                                                                                                                                |

| SOUT                  | Processor | Inhibits board selection.                                                                                                                                                |

| SMEMR                 | Processor | Allows output data drivers to be enabled on read. Inhibits clocked refresh during write operation.                                                                       |

| SWO                   | Processor | Inhibits spontaneous refresh during write operation.                                                                                                                     |

| PDBIN                 | Processor | Allows output drivers to be enabled on read.                                                                                                                             |

| PWR                   | Processor | When high at leading edge of MEMWRT, indicates a <u>front panel</u> write and requests a read so the front panel will display the new data.                              |

| PHANTOM<br>(optional) | Computer  | Inhibits board selection.                                                                                                                                                |

| PROT                  | Computer  | Write protects 16KRA if high and board is selected. (Wire it low if your machine doesn't provide it.)                                                                    |

| UNPROT                | Computer  | Unprotects 16KRA if high and board is selected.                                                                                                                          |

| DIØ-7                 | 16KRA     | Data delivered here after a read. Dri-<br>vers are enabled by BOARD SELECT and<br>PHANTOM and SMEMR and PDBIN.                                                           |

| PS                    | 16KRA     | Indicates selected board is write pro-<br>tected if low.                                                                                                                 |

| PRDY                  | 16KRA     | Indicates selected board is ready if high.                                                                                                                               |

Each match line corresponds to a page. A one (high) on any match line causes those of higher page number to be held at  $\emptyset$ , thus only one page can be enabled (that with the lowest page number) even though more than one switch set may match Al2-Al5. This feature allows the 16KRA board to be used in systems where less than 16K is needed.

During memory cycles, the four match lines are selected by the multiplexer (U42) to drive the four PAGE lines. The PAGE lines select one or none of four RAS drivers. The PAGE lines are or!ed together in pairs to enable one or none of the two groups of six memory address drivers.

Only half of the address inputs of the memory array are driven at any one time. This is done to reduce peak current surges in the memory array.

A section of U60 forms the signal SINP+SOUT. The four match lines are and'ed with this signal and OR'ed together onto one line by U43 and appear at U44-8 as BOARD SELECT. BOARD SELECT • PHANTOM enables the PS and PRDY drivers (U63-11).

U62-8 forms BOARD SELECT • SMEMR • PDBIN • PHANTOM which enables the DI Bus Drivers, sending the contents of the output register to the DI Bus only during read operations when this board is selected.

The binary  $\overline{WR}$  is clocked by the leading edge of MEMWRT. A low at  $\overline{WR}$  will result in a WRITE operation.  $\overline{WR}$  can be clocked low only if this board is selected and not write protected. The gates at U70-3, U61-3 and U63-8 provide the necessary signal at the  $\overline{R}$  input of the binary  $\overline{WR}$ .

# 5.3.2 Memory Array and Drivers

The memory array consists of 32 2104 4K dynamic IC's arranged in four groups of eight. Each 2104 can store 4096 bits, and each group of eight stores 4096 bytes.

The 2104 is a 16 pin package. Four pins provide power ( $\emptyset V$ . +5V, +12V, -5V). One pin connects data in and another connects data out. Six pins carry address data (12 bits in two six bit samples). The remaining four pins control memory operation. RAS provides selection and timing,  $\overline{CAS}$  provides timing,  $\overline{WE}$  selects read or write, and  $\overline{CS}$  (chip select) is wired to  $\emptyset V$  (enabled) since selection is being done by  $\overline{RAS}$ .

In the manufacturer's data some of these 12 signals are defined to be active low.  $(\overline{WE}, \overline{CS}, \overline{RAS}, \overline{CAS})$ . Others are defined active high, but all are arbitrary (six Addresses, Data In, Data Out).

In the 16KRA Module, all 12 signals at the memory pins are defined to be active low.

All memory inputs on the 16KRA Module are driven by special memory drivers (seven packages of 75365's). 2104's are nominally TTL compatible, but better noise margins are achieved by using external drivers.

# 5.3.3 Cycles

The timing of all six cycles (Read, Write, Refresh, Unserlected, Coincidence and Null) is identical. Each consists of a hominal 370 nsec active period and a nominal 150 nsec recovery period.

Either of two signals, MC or RC, can initiate a cycle. RC describes a refresh cycle and MC describes a read or write cycle.

MC and RC are or'ed in U61, with the output on pin 8 being applied to U71. U71 is a delay line with outputs which reproduce MC+RC delayed by 100 nsec (pin 14), 150 nsec (pin 4), 250 nsec (pin 12) and 350 nsec (pin 6). This is a passive delay line consisting of LC sections and TTL drivers built into the input and output lines.

These four delayed outputs are connected to a four-input nand gate (U57-6), the output of which is used to reset the binaries producing RC and MC. This reset will occur 350 nsec after the rise of RC or MC. RC+MC will then fall, and 100 nsec later U57-6 will rise again, releasing the resets of RC and MC.

The above cycle contains passive delays totaling 450 usec, and propagation delays through logic stages totaling 50 nsec min, 70 nsec typical. RC or MC will be on for about 370 nsec and off for about 150 nsec, giving a cycle duration of about 520 nsec.

Each cycle is described by the signal CY which is set to 1 at two propagation delays after the rise of MC+RC, and clocked to a  $\emptyset$  by the trailing (rising) edge of U57-6. Thus a cycle can be defined as the time during which CY is on.

MC+RC causes RAS (row address strobe) at the selected page of memory IC's. The signal WE (write enable) determines whether an MC is a read or a write. It controls the WE inputs to all memory IC's. The signal QU describes a failed attempt to perform a memory cycle. Presence of QU requests that another attempt at a memory cycle be made, and causes an unready (low on PRDY) if this board is selected.

The signal CAE (column address enable) is clocked to a 1 by the 100 nanosecond delay tap, only if MC is high. Its presence causes the address multiplexer to present the second group of six address lines to the memory address drivers. It is reset to  $\emptyset$  by the removal of MC+RC.

The signal CAS (column address strobe) is clocked to a 1 by the 150 nsec delay tap, unless RC and MC are both on. Its presence causes  $\overline{\text{CAS}}$  to be applied to all memory IC's. It is reset to  $\emptyset$  by the same signal which resets MC and RC.

In summary, a cycle starts with MC or RC. RAS comes on and samples the row address. At 100 nsec the column address is presented. At 150 nsec CAS usually comes on, sampling the column address, write enable, and the input data (DO Bus) if a write. At 350 nsec RAS and CAS are removed, and output data may be clocked to the output register. At 520 nsec a new cycle may start.

### Read Cycle

This normal cycle retrieves data from the indicated address. If SYNC or QU is present, the trailing edge of  $\emptyset 2$  clocks MC to a 1 to start a cycle. RC remains at  $\emptyset$ .  $\overline{RAS}$  occurs at the selected page of memory, causing the row address to be saved, and starting a cycle within each of eight memory IC's. CY goes to 1.

After 100 nsec CAE is clocked to a l. The column address is presented to the memory address drivers.

After 150 nsec, CAS is clocked to a l. CAS occurs at all memory IC's, causing all to release their data output to the third state. Within the eight memory IC's selected by RAS, the column address is saved, and WE is sampled. This is a read cycle, so WE is high, and the input data is ignored. At some time before 350 nsec from the start, each of the eight selected chips will enable its output pin which will contain valid data.

After 350 nsec, reset occurs and both MC and CAS become  $\emptyset$ . RAS is removed and CAE becomes  $\emptyset$ . Output data is clocked to the output register and enabled to the DI Bus (if this board is selected, and SMEMR and DBIN are high).

After 520 nsec, CY goes to  $\emptyset$  and a new cycle may start.

## Write Cycle

This normal cycle stores data at the indicated address.

The signal WE becomes a l. This causes MC to become a l to start a cycle.  $\overline{RAS}$  occurs at the selected page of memory, causing the row address to be saved and starting a cycle within each of the eight selected memory IC's. CY becomes a l. RC remains at  $\emptyset$ .

After 100 nsec CAE is clocked to a l. The column address is presented to the memory address drivers.

5-6 16KRA

After 150 nsec CAS is clocked to a l. CAS occurs at all memory IC's, causing all to release their data outputs to the third state. Within the eight memory IC's selected by  $\overline{\text{RAS}}$ , the column address is saved, and  $\overline{\text{WE}}$  is sampled.  $\overline{\text{WE}}$  is found to be low. Sometime before 350 nsec, the input data will be stored at the indicated address. At some other time before 350 nsec, the selected eight memory IC's will enable their outputs, and present l's there.

After 350 nsec, reset occurs. MC, CAS, and WE become  $\emptyset$ . RAS is removed, CAE becomes  $\emptyset$ . Output data (all l's) is clocked to the output register, but not enabled to the DI Bus since SMEMR and PDBIN are low.

After 520 nsec CY becomes a  $\emptyset$  and a new cycle may start.

## Refresh Cycle

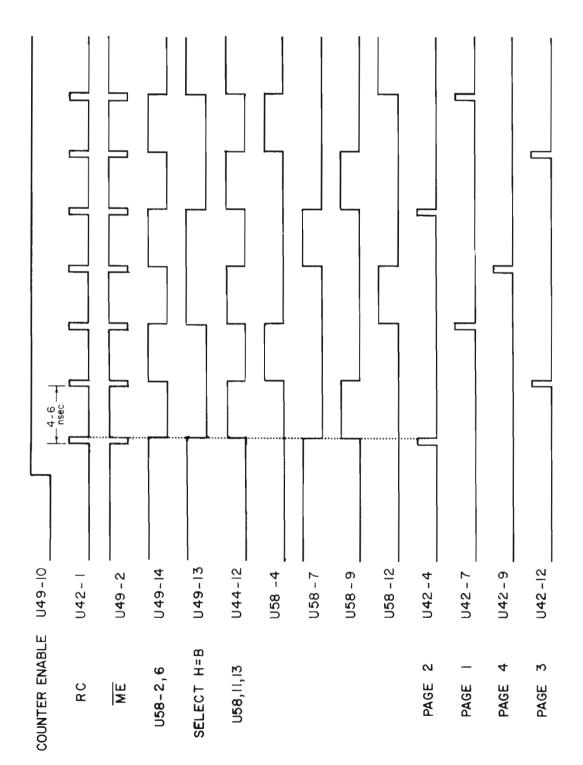

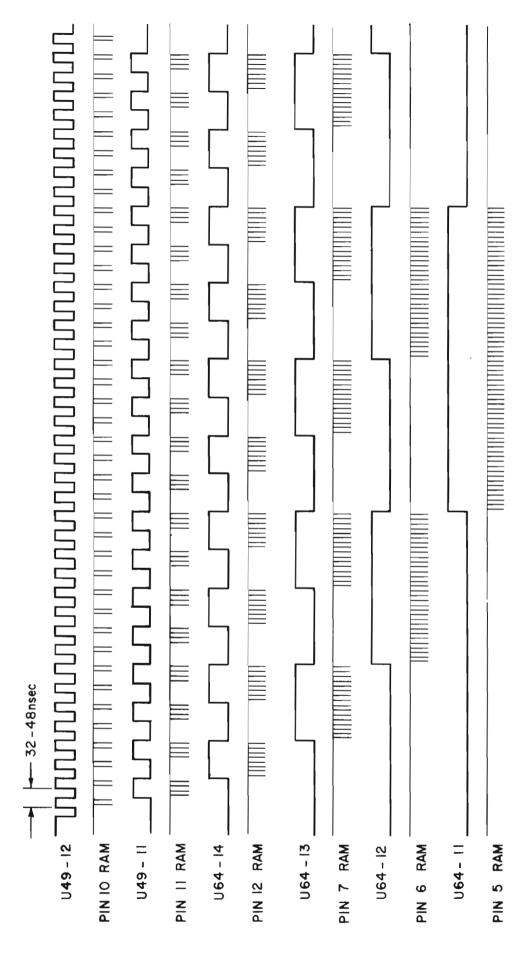

This normal cycle refreshes the data in one row in the eight memory IC's of one page. Since there are 64 rows in each IC, and four pages on this board, a complete refresh will require 256 refresh cycles. The eight bit refresh counter (U49,U64) indicates one of these 256 states.

RC becomes a 1. The address multiplexer selects the high order six bits of the refresh counter as the source of address for the memory address drivers. The page multiplexer selects the four outputs of U58 as the source of data for the page lines (instead of the match lines). U58 enables one of four lines selected by the two least significant bits of the refresh counter.

RAS occurs at the selected page of memory, causing the row address (from the refresh counter) to be saved, and starting a cycle within each of the eight selected memory IC's. CY becomes a l.

After 100 nsec CAE is clocked, but does not go to 1 since MC is low. The address multiplexer continues to present the row address.

After 150 nsec,  $\overline{\text{CAS}}$  is clocked to a 1. CAS occurs at all memory IC's, causing all to release their data outputs to the third state. The column address is saved and  $\overline{\text{WE}}$  is sampled and found to be high. Input data is ignored. Before 350 nsec the data described (which is irrelevant) is presented at the outputs.

After 350 nsec, reset occurs. RC and CAS become  $\emptyset$ . RAS is removed, CAE is already  $\emptyset$ , so  $\overline{\text{CAE}}$  is high, and the refresh counter counts 1.  $\overline{\text{CAE}}$ , being high already, does not rise, so the output data is not clocked to the output register. The output data remains the same.

After 520 nsec, CY becomes  $\emptyset$ , and a new cycle may start.

To the Memory IC's selected, this seems to be a normal read cycle. They are designed to refresh all data within a row each time that row is accessed by a RAS, regardless of the details of a cycle.

## Unselected Cycle (CAS only cycle)

This normal cycle has no external purpose. It is the result of the method used to accomplish refresh.

If SYNC or QU is present, the trailing edge of  $\emptyset 2$  clocks MC to 1 to start a cycle. RC remains at  $\emptyset$ . The address does not represent any page on this board, so no page is selected, and BOARD SELECT is low.

Since no page is selected, no memory chips receive RAS, none start a cycle.

After 100 nsec CAE is clocked to a l. The column address is presented to the address drivers.

After 150 nsec, CAS is clocked to 1 and  $\overline{\text{CAS}}$  occurs at all memory IC's, causing all to release their data outputs to the third state. No memory IC's have been started by  $\overline{\text{RAS}}$ , so no address storage and read occur.  $\overline{\text{WE}}$  is high, but isn't used anyway.

After 350 nsec, reset occurs, MC and CAS become  $\emptyset$ . CAE becomes  $\emptyset$ . The output pins are third state and this indeterminate data is clocked to the output register destroying the previous data. The output does not get enabled to the DI Bus because this board is not selected.

After 520 nsec, CY goes to  $\emptyset$ , and a new cycle may start.

## Coincidence Cycle

This is an abnormal cycle which occurs when two asynchronous requests for memory occur at times such as to set both RC and MC to 1 at approximately the same time.

Normally RC and MC do not both occur in one cycle, since the presence of each is intended to prevent the other. Due to propagation delays, it is impossible to make them totally mutually exclusive, however, it is guaranteed that if both are to occur, the second will follow the first by only a few stage delays (typically less than 50 nsec). The COINCIDENCE CYCLE is an example of this.

RC or MC occurs. Before inhibition is complete the other of RC or MC occurs. Subsequent events in the cycle are timed by the first of the two. WE may be in either state.

5-8 16KRA

RAS occurs at the selected page of memory, causing the row address to be saved and starting cycles in these eight memory IC's. Shortly after both RC and MC = 1,  $\overline{RC} \bullet \overline{MC}$  becomes a  $\emptyset$ . This signal forces QU to 1, indicating a failed attempt and a request for a new attempt. QU causes PRDY to go low since this board is selected.

After 100 nsec, CAE is clocked to a 1 and column address  $\emptyset$  is presented to the memory drivers.

After 150 nsec, CAS is clocked, but it does not go to 1 since its J input ( $\overline{MC} \bullet \overline{RC}$ ) is low. No  $\overline{CAS}$  occurs. The memory IC's selected by  $\overline{RAS}$  execute a RAS only cycle. This refreshes some row of memory and has no consequences external to the memory IC's.  $\overline{WE}$  does not get sampled, and no memory chips change the state of their outputs.

After 350 nsec, reset occurs. MC, RC become  $\emptyset$ . RAS is removed. Since CAE is low, the refresh counter does not advance. (Coincidence cycle is not counted as a good refresh.) CAE is reset to  $\emptyset$ , clocking unknown data into the output register which is enabled to the DI Bus. (The processor or DMA device must observe the low on the PRDY line. This is bad data.)

After 520 nsec, CY goes to  $\emptyset$  and a new cycle may start. Note that if the coincidence cycle started at a  $\emptyset$ 2 trailing edge, then the next  $\emptyset$ 2 trailing edge has already occurred. In this case, QU remains set and the next subsequent  $\emptyset$ 2 trailing edge will start a new cycle. Thus a coincidence cycle may cause two consecutive wait states.

## Null Cycle

The NULL Cycle is a coincidence cycle which is also an unselected cycle.

Both RC and MC occur at approximately the same time. The address does not represent any page on this board, so all four match lines, and BOARD SELECT are low. The row address chosen is the refresh address, so one page line (from the refresh counter via U58) is high.  $\overline{RAS}$  occurs at the selected eight memory IC's, causing each to store the row address and start a memory cycle. Shortly after MC and RC become a 1,  $\overline{MC} \circ \overline{RC}$  becomes a  $\emptyset$ , and sets QU to a 1, indicating a failed attempt and a request for a new attempt. QU does not cause PRDY to go low since this board is not selected. This is the difference between a NULL CYCLE and a COINCIDENCE CYCLE.

After 100 nsec, CAE is clocked to a 1. Column address  $\emptyset$  is presented to the memory drivers.

After 150 nsec, CAS is clocked, but is does not go to  $\emptyset$  since its J input ( $\overline{RC} \bullet \overline{MC}$ ) is low. No CAS occurs. The memory IC's selected by RAS execute a RAS only cycle. This refreshes some row of memory and has no consequences external to the memory IC's.  $\overline{WE}$  does not get sampled, and no memory chips change the state of their outputs.

After 350 nsec, reset occurs. MC and RC become  $\emptyset$ . RAS is removed. Since  $\overline{\text{CAE}}$  is low, the refresh counter does not advance. (The NULL CYCLE is not counted as a good refresh.) CAE is reset to  $\emptyset$ , clocking unknown data into the output register which is not enabled to the output bus since this board is not selected. (This bad data may appear on the DI Bus next time this board is selected, but it will be replaced by the requested data during that cycle.)

After 520 nsec, CY goes to  $\emptyset$  and a new cycle may start.

The QU caused by a NULL CYCLE remains only for the duration of SYNC. PRDY does not go low since this board is not selected.

## 5.3.4 Operations

An operation is a group of one or more cycles which achieves a desired result.

There are four intended operations. They are: READ, READY WRITE, UNREADY WRITE, and SPONTANEOUS REFRESH.

Many other operation types occur, but all are variations of these intended operations which arrive at their intended result by an abnormal sequence because of the occurrence of an abnormal cycle (COINCIDENCE or NULL CYCLE), or because of deselection from one of several sources.

## Read Operation

SYNC occurs. It remains for 1 clock period, rising after a  $\emptyset$ 2 leading edge, and falling after the next  $\emptyset$ 2 leading edge. To the 16KRA module, SYNC is a request for an operation.

The  $\emptyset 2$  trailing edge during SYNC clocks MC to a 1 to start a READ CYCLE,

Soon PDBIN and SMEMR become 1, defining this as a READ operation. About 400 nsec after the  $\emptyset 2$  trailing edge, the data from memory appears on the DI Bus.

The trailing edge of SYNC clocks SR to a 1 since its J input (SMEMR) is high, requesting a RESET CYCLE.

At 500 usec or before, the next  $\emptyset 2$  trailing edge finds SYNC removed and does not set MC. At 520 nsec, CY is reset, and the trailing edge of  $\overline{\text{CY}}$  clocks RC to a 1, starting the requested RESET CYCLE. SR is reset to  $\emptyset$ . At 1040 nsec the refresh cycle ends. CY is reset to  $\emptyset$ , and the READ operation is complete.

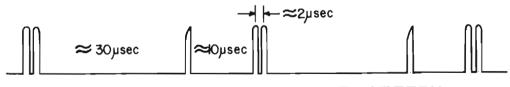

Note that the READ operation accomplished the requested memory read, and also did one refresh. When controlled by an 8080 with a Ø2 rate of 2 MHz, the refresh cycles which occur in read operations provide all the refresh required, and no wait states occur. Operation at Ø2 rates greater than 3 cycles per 1040 nsec (2.88 MHz) will cause wait states to occur.

## Ready Write Operation

READY WRITE is the normal operation for placing data in memory. It occurs with the processor or DMA device active (sending SYNCS).

SYNC occurs. It rises after a  $\emptyset2$  leading edge and falls after the next  $\emptyset2$  leading edge. To the 16KRA module, SYNC is a request for an operation. The  $\emptyset2$  trailing edge during SYNC clocks MC to a 1 to start a READ CYCLE. SMEMR and PDBIN do not rise; therefore the data read from memory appears in the output register, but not on the DI Bus.

At 520 nsec, CY will become  $\emptyset$ , ending the read cycle.

At some time before or after 520 nsec, PWR will go low to cause MEMWRT to become a l. If this board is selected, unprotected, and PHANTOM is a l, the leading edge of MEMWRT will set  $\overline{WR}$  to  $\emptyset$ . MEMWRT must be present for about 50 nsec or longer to do this. This is because of the slow rise of the signal at the clock input of  $\overline{WR}$ . It has been deliberately loaded with a capacitor (C48) to prevent write cycles from originating from noise spikes on MEMWRT.

WR • CY is applied to the clock input of WE. If no cycle is in progress, WE is clocked by the leading edge of WR. If the read cycle is still in progress when WR rises, WF is clocked by the trailing edge of the cycle. WE is clocked to a l, and sets MC to a l to start a WRITE CYCLE.

At about 520 nsec after WE is clocked, CY becomes  $\emptyset$ , ending the write cycle and the READY WRITE OPERATION.

The timing of PWR in the READY WRITE operation is likely to determine the maximum Ø2 frequency which the 16KRA module can serve without causing wait states. If PWR comes early enough, this could be equal to the similar frequency limit for read operations (3 cycles per 1040 nsec, or 2.88 MHz). PWR will probably not come this early and the frequency limit for READY WRITE will probably be lower.

5-11 16KRA

Note that at the trailing edge of SYNC, SR was clocked but remained a  $\emptyset$  since SMEMR was low. The trailing edge of CY clocks RC, but it remains a  $\emptyset$  since SR is  $\emptyset$ . No refresh cycle occurs during the READY WRITE operation.

## Unready Write Operation

The UNREADY WRITE operation is the normal sequence for storing data in memory from the front panel of an Sl00 microcomputer.

These machines provide a "RUN/STOP" switch. When STOP is used, the front panel sends an unready signal (typically XRDY low).

Memory write from the front panel is done by operating a "DEPOSIT" Switch which ultimately fires a deposit oneshot which pulses MEMWRT. Before and during this MEMWRT pulse, the 8080 is in WAIT, and there are no SYNC pulses.

If this board is selected, unprotected, and PHANTOM is a 1, the leading edge of MEMWRT will charge the capacitor at the clock input of WR, and if MEMWRT is long enough it will set WR to a 1.

WE will be clocked to a 1, setting MC and starting a WRITE CYCLE.

At the leading edge of MEMWRT, PWR is high since this MEMWRT is caused by DEPOSIT, and the processor is in WAIT. The leading edge of WR clocks SQ to a l. This sets QU to a l to request a read cycle. PRDY goes low, but this doesn't matter since XRDY is already low.

At the first  $\emptyset 2$  trailing edge after the WRITE CYCLE is complete, MC is clocked to 1 to start a READ CYCLE, and QU is clocked to  $\emptyset$ , raising PRDY.

This read cycle places the data just stored on the DI Bus for display on the front panel.

Since there was no SYNC, no RC results.

#### Spontaneous Refresh Operation

At any time that there has been no RC for 6 usec, current thru Rl2 will have charged capacitor C46 to a voltage high enough to fire the Schmidt trigger, U62-6. This will set RC to a 1, starting a refresh cycle.

Presence of a 1 on RC causes Q1 to discharge C46 which resets the 6 usec timeout.

The SPONTANEOUS REFRESH operation consists of only 1 cycle, a refresh cycle.

## Other Types of Operations

The four operations just described represent the four intended operations in their simplest forms. Each is subject to variations due to asynchronous coincidence with one of the others, and some have variations due to factors such as deselection by BOARD SELECT, PHANTOM and WRITE PROTECT Detailed descriptions of these variations is beyond the scope of this manual.

#### 5.4 REFRESH

Refresh is normally accomplished by the READ operation which slips a refresh cycle in after each memory read access. When the computer is running, executing normal 8080 code, read operations are attempted so often that no spontaneous refresh operations ever occur. This is true because all instruction fetches are read operations.

When no read operation has been requested for 6 usec, a spontaneous refresh will occur. This may happen during WAIT (front panel operation), HOLD, or HALT (or when the computer is off if this board is battery supported).

A spontaneous refresh will occur every 6 usec as long as normal operation is suspended.

When normal operation is resumed, a coincidence with a read or write request may occur, and this may result in one or two wait states as described above

Direct Memory Access (DMA) is accomplished by a DMA controller which requests HOLD. The processor sends PHLDA when ready and stops operation. The DMA device then disables the processor from the bus, enables itself to the bus, and usurps the role of the CPU. The usual object of this is to transfer a large block of data between some external device and memory

In general, the 16KRA will operate satisfactorily with DMA devices which obey the normal 8080 conventions. Due to the large variety of possible DMA devices, we recommend that compatibility of any specific DMA device be verified.

Jumper option D (Area D) allows the choice of two options, DN (normal), and DR (Reset).

Normally option DN is used. The refresh 6 usec timer is reset to  $\emptyset$  at every refresh cycle. A DMA device which sends no read request for 6 usec will encounter a wait state while refresh is being done.

If option DR is used, the refresh timer is reset to  $\emptyset$  after refresh cycles; and also after read and write cycles. A DMA device which sends a read or write request every 6 usec will not encounter wait states.

Loss of refresh may occur on long DMA transfers containing no read requests.

The DR option makes it possible to use write only DMA devices which will not tolerate a wait for refresh. Note that if DR is used, the DMA device or the program must assume responsibility for refresh.

5-14 16KRA

# SECTION VI

# DRAWINGS

16KRA DYNAMIC READ/WRITE MEMORY MODULE

|  |  | *             |

|--|--|---------------|

|  |  | ,             |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  | ,             |

|  |  |               |

|  |  |               |

|  |  | $\overline{}$ |

|  |  |               |

|  |  |               |

|  |  |               |

|  |  | ŧ |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | 8 |

|  |  |   |

|  |  |   |

|  |  |   |

| 1      |

|--------|

|        |

| *      |

|        |

|        |

|        |

|        |

|        |

| $\sim$ |

|        |

|        |

|        |

|        |

|        |

| ,      |

|        |

| 5      |

|        |

|        |

|        |

|        |

|        |

|        |

S-100 BUS ADDRESS LINES

S-100 BUS CONTROL & STATUS LINES

( Jan 1 ) And 1

.

# SECTION VII

# DIAGNOSTIC TEST

16KRA DYNAMIC READ/WRITE MEMORY MODULE

#### 7.1 INTRODUCTION

#### 7.1.1 General

The 16kkA Diagnostic Test (16kDT) checks a 16kRA Dynamic Read/Write Memory Module (16kRA) addressed at 4000 hexadecimal (hex) as a 16k continuous block. It contains four different tests which are described in this section (7.1). The rest of Section 7 contains the trouble-shooting procedures using these tests and additional theory of operation.

The four tests are contained on a CUTS format cassette tape which has been supplied to all Processor Technology dealers. These tests are not copyrighted and may be duplicated by 16KRA owners at the store which originally sold the board.

#### 7.1.2 Data Path Test

The Data Path Test checks the logic which carries data through the board. To accomplish this it writes and reads back a "marching" pattern at one address only. This address is normally 4000 Hex, but any address may be specified by entering the desired address, a space, and an asterisk at the appropriate point in the test. (Example: 4567 \* <CR>) This will run the Data Path Test at address 4567 Hex. The display shows three columns of eight-bit words. Each word in the display represents the contents of the byte at the specified address.

The left column shows a sequence of sixteen words which were written during the brief period of the test. The first word at the top snows all zeros, the second word from the top contains all zeros except the right-most bit. The third word contains all zeros except the two right-most bits. Going down the column in this manner, the ninth word has all ones. Then zeros start appearing at the right end of the word, one bit per word. Finally, the last word at the bottom contains all zeros. Thus, eight ones have "marched" across the column, representing the flow of ones through the byte at address 4000 Hex or the specified address.

The middle column shows the words which were read back. If the 16KRA is working properly, the words read back are identical to the words being written. The right column on the display marks with an "X" those bits which are not identical. Identical bits are indicated by a "-".

## 7.1.3 Addressing Test

The Addressing Test checks for non-functional address lines, using the results of the Data Path Test. Since it relies on these results, it may only be run immediately following the Data Path Test. The test first writes ones in all working bits

at location 4000 Hex, then writes zeros to the first address given in Table 7-1. Each of the addresses in Table 7-1 differs from address 4000 Hex in only one address bit. If the address line which controls this bit is bad, then location 4000 Hex will be written to instead of the specified address. By checking to see if any working bit at address 4000 Hex has changed to zero, the test identifies non-functional address lines. By writing to all the addresses in Table 7-1, all address lines are checked. The display indicates which address lines are bad when the test is complete.

Table 7-1. Test Addresses

| ADDRESS | LINE | ADDRESS | (HEX) | ADDRESS | LINE | ADDRESS ( | (HEX) |

|---------|------|---------|-------|---------|------|-----------|-------|

| ΑC      | )    | 4001H   |       | A7      |      | 4080Н     |       |

| Al      |      | 4002H   |       | A8      |      | 4100Н     |       |

| A 2     | 2    | 4004H   |       | A9      |      | 4200Н     |       |

| A 3     | }    | 4008H   |       | Al      | 0    | 4400Н     |       |

| A 4     | ·    | 4010H   |       | A1:     | l    | 4800Н     |       |

| A S     | 5    | 4020H   |       | A1      | 2    | 5000Н     |       |

| Αe      | 5    | 4040H   |       | A1      | 3    | 6000Н     |       |

The Addressing Test is designed to find address lines which are shorted or open before they reach the RAM drivers, and to find bad drivers or bad address multiplexers. Shorts in the address lines occurring after the RAM drivers will not usually be detected by the test, for the following reason. When two address lines are shorted, and one of the lines is low, the low line will usually pull the other line low also. The test addresses used by the Addressing Test, after inversion by the RAM address drivers, consist of one low bit in a field of high bits. If a short occurs between two address lines at this point, both lines will go low, generating an address other than 4000 Hex, so that no bits at that address are changed.

## 7.1.4 Exerciser

The Exerciser program writes and reads a specified byte of data at a specified address. At the time when the Exerciser program appears, there is an option to run the Data Path Test at a specified address.

#### 7.1.5 Numbered Test Selection

This feature allows selection of any of the tests after the Exerciser has been run.

## 7.2 INTRODUCTION TO TEST PROCEDURE

This test procedure is designed for use with a Sol system. It is dependent upon the 16KDT diagnostic test cassette. Also, a dual-trace scope with a delayed sweep will be necessary.

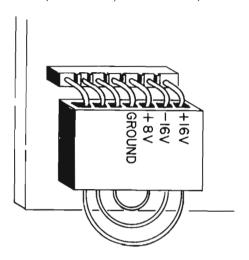

Before the board is plugged into the S-100 bus it is necessary to check for power supply shorts. Use an ohm-meter that is set to a scale which will show 100 ohms clearly. Position the board with the ICs up and the S-100 bus towards you. In the lower left corner is a brown connector plug with 3 jumper wires on it. (See Figure 7-1.)

Figure 7-1. CONNECTOR JUMPERS

Connect the negative probe of the ohmmeter to the center pin (GND). Be sure the voltage at the ohmmeter probes is the same as the marked polarity. To check this, use a common diode of any type. The ohmmeter will show a low resistance when the negative lead is connected to the end of the diode with the dark band near it. Frequently, ohmmeters will have the polarity reversed so it is important to check.

With the negative probe connected to the center, ground pin, touch the positive probe to the right three pins, one at a time. All of the readings should be greater than 100 ohms. Next measure between the +8V and -16V, the +8V and the +16V, and finally between the -16V and +16V. The polarity of the probes is not important for the last three measurements. If any of the readings were less than 100 ohms, the board should not be plugged into the S-100 bus until the cause is determined and corrected.

This preceding procedure will show any shorts before the voltage regulators, such as shorted capacitors, shorted regulators, or shorts between traces (usually solder bridges). It is also necessary to check for shorts on the regulated side of the voltage regulators. This can be done by measuring at the pins of any RAM chip. Table 7-2 lists the required resistance readings. "Positive Probe" in the table means the probe supplying positive voltage.

Table 7-2. Resistance Measurements at RAM Pins

| Positive | Negative | Approximate |

|----------|----------|-------------|

| Probe    | Probe    | Resistance  |

| pin 16   | pin 9    | 8 ohms      |

| pin 16   | pin 8    | 13          |

| pin 16   | pin 1    | 500         |

| pin 1    | pin 16   | 8           |

| pin 8    | pin 16   | 100         |

| pin 9    | pin 16   | 30          |

| pin 9    | pin 8    | 150         |

| pin 8    | pin 9    | 75          |

If any of the preceding readings are much lower than indicated in Table 7-2, it can be assumed that a problem exists on the board. At this point, a check should be made to see that all IC types correspond to the 16KRA Assembly Drawing (page VI-1) and that pin 1 of each IC is in the indicated position.

Also inspect the back of the board to see if any blobs of solder bridge two adjacent pins or traces. These can be removed with a soldering iron. If any shorts cannot be visually located, it will be necessary to use a DVM with a low ohms scale to find the short.

If the preliminary resistance checks are found acceptable, the board is ready to be plugged into a S-100 bus connector. Insert the board with the power off and connect a voltmeter between ground (pin 16) and +5V (pin 9) on any RAM chip. Turn on the power and immediately read the voltage. If it is not 4.75 to 5.25V turn off the power immediately. Repeat the procedure with pin 8 (+12V) and pin 1 (-5V). If these voltages are not within 1/2 volt of the nominal value, remove the board from the system until the cause is determined. If these voltages check OK, leave the power on but check for overheating of the regulators. They should not be too hot to touch. Check if any individual ICs are hot to the touch. If any are found, they can be presumed defective.

Now, look at the screen of the video display. Do the cursor and prompt look right? If so, proceed to the next section. If any other characters have appeared, the board has "crashed the bus", or interfered with the operation of the rest of the system.

#### 7.4 THE 16KDT TEST

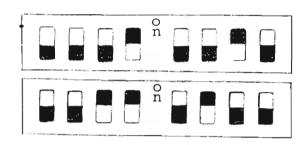

If the cursor and prompt have appeared properly, with no other characters displayed, address the switches as 4, 5, 6, and 7 as shown in Figure 7-2. Before attempting to load the test, make sure that there is at least 1K Hex of memory addressed as a block starting at zero. The test is not relocatable.

Figure 7-2. ADDRESS SWITCH POSITIONS

To load the cassette, first type CA <CR>, to activate the cassette motor, and rewind the cassette. Next type the Mode Select Key to return to command mode. The command XEQ <CR>> will now load in the tape and cause the tape to stop when done. The Data Path Test should appear on the screen. Press the space bar to procede. Study the display carefully. The left column shows what was written, the center column shows what was read back, and the right column marks any differences between the two. Are there any observable patterns? Are there X's centered in a particular column? Does any column have all ones or zeros read from it? Are the errors random? Are all ones or zeros read from memory? The display is organized with bit 7 on the left and bit 0 on the right as a binary number would be written. Press the space bar twice again. Study the display. Are any of the address lines indicated defective?

To use the Exerciser, enter a number between 4000-7FFF hex and the data to be written. The data is written into memory as one byte of 8 bits, derived from the two hexadecimal data characters entered. Entering 00 Hex for data writes a byte of all zeros; FF writes all ones. A typical entry might be 4000 FF <CR>. To stop the Exerciser, press the Escape key. At this point a choice of any of the four tests or a return to SOLOS can be made.

If no errors are found in #4, the Memory Test, press Escape to continue. If an error is found, the address of the bad byte will be displayed. Since the test can only find one bad byte at a time, repeat the test until no errors are displayed. To further pinpoint the error, dump nearby memory using the command DU <low address> <high address>. Select the addresses for this command to include the error, but not to exceed the capacity of the video display, 240 decimal bytes. If the error occurred at 4567 for example, dump address 4500 to 45EF. Usually a dump from XX00 to XXEF will include the error. When running the memory test, the following data pattern is written into successive locations in memory: 00, 01, 02, 04, 08, 10, 20, 40, 80, 00, etc. When examining a dump in the vicinity of an error, look for irregularities in this pattern. For example, if the

dump shows an area containing 00, 01, 02, 04, 08, 10, 22, 40, 80, the 22 is incorrect. To locate the bad bit at this location convert both the correct and incorrect data words into binary patterns. The correct word 20 is 00100000; the incorrect word 22 is 00100010. Thus the error is in bit one, the second from from the right.

If many errors are revealed by a dump, it is likely the problem is not bad storage locations in RAM chips. Instead look for timing problems. See Section 7.5 below.

The memory on the card is organized as 4 pages. Each page contains 1000 Hex (4K decimal) bytes of data. Each RAM chip is a 4K by one-bit storage so there is one RAM chip used to store one bit of data per byte. Eight chips are thus used to store the eight bits in one data byte. Figure 2-1, page II-3, relates the chip location to the page and bit location.

### 7.5 OVERVIEW

Figure 7-3 presents the timing relationships during the typical operation of the 16KRA. All of the signals shown are critical to the proper operation. A quick check of these signals, using the procedures given later, will often reveal the source of the malfunction. To the left of Figure 7-3 is a column giving the names of the signals shown, as they appear on the schematic and block diagrams. The second column gives an IC pin number where the signal may be found. Three signals: 22 CLOCK, SYNC, and MEMWRT, come from the processor, via the S-100 bus. A brief description of the remaining signals, which are all generated on the 16KRA board, is given below.

#### 7.5.1 BOARD SELECT

This signal indicates that the processor has put the address on the address bus and that the page selection circuitry has found a match between the high order 4 bits of address and one of the four page address assignment switches. The first BOARD SELECT occurs when the processor is writing to the 16KRA. The second one occurs when it is reading the data back to the 16KRA.

## 7.5.2 MC